Systemverilog 中`include 和 filelist区别

记录今天在搭建验证平台时遇到的一个问题,问题简单描述:搭建的是验证CPU core block的平台,对于core dut来说包括很多小模块,如decode、rename、dispatch、issue和各种FU等模块,针对于每个小模块写了reference_model,需要加到top中,但是由于多个人负责各个子模块的验证工作,所以直接写到top中是不方便的,需要改来改去,所以最终是通过在top中include文件的方式来进行处理。

我负责的include模块如下所示:

因为需要往RM灌入激励,但是对于core 模块的中间小模块来说,激励是中间信号,因此直接采用层次“点”的形式直接抓DUT输入信号。

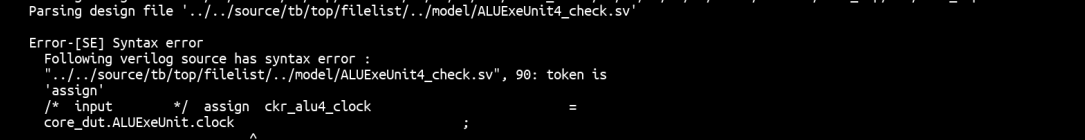

但是此时编译时报如下错误:上图第90行有语法错误。

检查语法发现没有问题,那就很奇怪了,卡了半天后。在top中去掉该include文件发现神奇的事情,重新编译还报相同的错误。检查了filelist后发现加了这个check文件,那么问题几乎可以定位了,在编译时会首先编译filelist中的文件,但是对于该文件中,使用了层次“点”的形式抓取了信号,但是此时还没建立UVM树结构,因此会报错误,但是吐槽一下VCS工具,报的是语法错误,让我在那里检查半天语法。发现问题后,就解决问题,在filelist中去掉该check文件,通过+incdir+dir的方式,发现编译过了。

总结一下:

1.工具编译时会首先编译filelist里面的东西,说到filelist简单说下-f和-F的区别,-f编译时filelist的路径相对于Makefile在的路径为参考路径,-F编译时是以filelist本级路径为参考路径,所以-F比较方便。

2.include其实就相当于整体文件插入,那么就和include前面代码和后面代码有关系了,提前编译会出错的,编译遇见include文件时会去+incdir库里面寻找。