Cortex-M0的内核架构

目录

Cortex-M 系列产品线

Cortex-M系列是由ARM(Advanced RISC Machines)开发的一系列32位微控制器(MCU)内核。以下是Cortex-M系列的一些常见产品线:

- Cortex-M0: 这是Cortex-M系列中的最基础、最低功耗的处理器内核。它适用于对成本和功耗要求极高的应用,如传感器、嵌入式控制器等。

- Cortex-M0+: Cortex-M0+是对Cortex-M0内核的改进版本,提供了更高的性能和更低的功耗。它特别适用于资源受限的应用,如物联网设备、传感器节点等。

- Cortex-M1: Cortex-M1是ARM的较早的FPGA(现场可编程门阵列)友好型内核,主要用于在FPGA上实现可编程逻辑控制器。

- Cortex-M3: Cortex-M3是一款功能更强大的处理器内核,具有更高的性能和更多的外设接口。它适用于需要较高计算能力和实时控制的应用,如工业自动化、汽车电子等。

- Cortex-M4: Cortex-M4在Cortex-M3的基础上增加了数字信号处理(DSP)扩展指令集和浮点单元(FPU),使其更适合于音频处理、图像处理和其他需要高性能数字信号处理的应用。

- Cortex-M7: Cortex-M7是Cortex-M系列中最强大的内核,具有更高的时钟频率和更高的性能。它适用于要求实时性和高计算能力的应用,如无人机、工业控制等。

- Cortex-M23: Cortex-M23是ARM推出的针对物联网设备和安全性设计的内核。它具有较低的功耗、较小的面积和较高的安全性,适用于需要高度安全性和低功耗的应用,如智能门锁、传感器网络等。

- Cortex-M33: Cortex-M33是在Cortex-M23的基础上增加了一些额外功能的内核,如TrustZone技术和数字信号处理(DSP)扩展指令集。它适用于对安全性要求更高的应用,如智能卡、安全传输设备等。

这些是Cortex-M系列的一些常见产品线,每个产品线都具有不同的特性和适用范围,可以根据具体应用的需求选择适合的处理器内核。

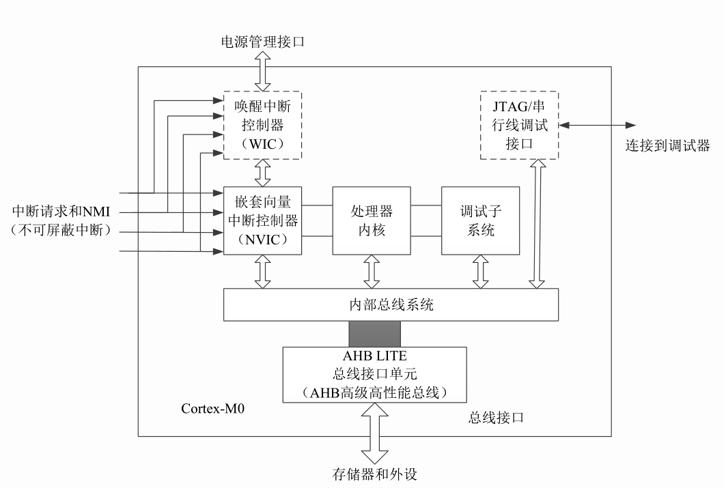

Cortex-M0结构框图

Cortex-M0 微处理器主要包括处理器内核、嵌套向量中断控制器(NVIC)、调试子系统、内部总线系统构成。

- 处理器内核

- 嵌套向量中断控制器(NVIC)

- NVIC的主要功能是接收和分发中断信号,并确定哪个中断具有优先级,并在适当的时候触发相应的中断服务程序(Interrupt Service Routine,ISR)。当多个中断同时发生时,NVIC通过优先级来确定哪个中断应该被处理。较高优先级的中断将立即中断正在执行的任务,而较低优先级的中断将等待。

- NVIC支持嵌套中断,这意味着当一个中断正在处理时,如果更高优先级的中断发生,处理器可以立即切换到更高优先级的中断服务程序,而不会中断正在执行的较低优先级的中断服务程序。一旦较高优先级的中断完成处理,处理器将返回到先前的中断服务程序继续执行。

- 调试子系统

- 调试子系统通常包含以下功能和工具:

- 调试器(Debugger):提供了一个交互式的开发环境,允许开发人员逐步执行程序、观察变量和数据、设置断点(Breakpoint)以及跟踪代码的执行流程。调试器能够帮助开发人员找到代码中的错误和问题,并对程序行为进行分析和调试。

- 分析工具(Analyzer):用于分析系统的行为和性能。这些工具可以帮助开发人员对系统进行性能优化、内存泄漏检测、代码覆盖率分析等。分析工具能够提供详细的报告和统计数据,帮助开发人员深入了解系统的性能和效率。

- 追踪器(Tracer):用于跟踪程序的执行过程和数据流动。追踪器可以记录程序执行的路径、函数调用关系、变量的取值等信息,以帮助开发人员理解程序的执行流程和数据交互,从而更容易地发现和解决问题。

- 监视器(Monitor):用于监测系统的状态和行为。它可以提供关于系统性能、资源利用情况、内存使用情况等方面的信息。监视器可以帮助开发人员了解系统的运行状况,识别性能瓶颈和资源消耗问题。

- 调试子系统通常包含以下功能和工具:

- 内部总线系统

- 嵌入式系统的内部总线系统是指用于在嵌入式设备内部连接各个组件和子系统的通信架构。内部总线系统允许不同的硬件模块相互通信和交换数据,以实现设备的功能。

- 内部总线系统通常由一组电子线路和协议组成,用于传输数据、控制信号和时序信息。这些线路和协议定义了数据传输的规则和格式,以确保各个组件之间的正确通信。

- 内部总线系统在嵌入式系统中扮演着关键的角色,它能够连接处理器、内存、输入/输出接口、传感器、执行器和其他外设等各种硬件模块。通过内部总线系统,这些模块可以相互协作,共享数据和资源,并实现系统的功能。

- 常见的嵌入式内部总线系统包括I2C(Inter-Integrated Circuit)、SPI(Serial Peripheral Interface)、CAN(Controller Area Network)、USB(Universal Serial Bus)等。这些总线系统在不同的嵌入式系统中具有不同的应用和特点,可以根据具体的需求选择适合的总线系统来设计和实现嵌入式设备。

Cortex-M0 微处理器通过精简的高性能总线(AHB-LITE)与外部进行通信。

Cortex-M0特性

- 采用Thumb指令集 (ARM指令是32位的,而Thumb指令时16位的,如果存储空间中可以放32条ARM指令,就可以放64条Thumb指令,因此在存放Thunb指令时,代码密度高)

- 高性能,使用ARMv6-M的体系架构;

- 中断数量可配置1-32个,4级中断优先级。

- 门电路少,低功耗。中断唤醒控制器(WIC),支持极低功耗休眠模式。

- 兼容性好。与Cortex-M1 处理器兼容,向上兼容 Cortex-M3 和 Cortex-M4 处理器 ,可以很容易地升级、移植。

- 支持多种嵌入式操作系统,也被多种开发组件支持。

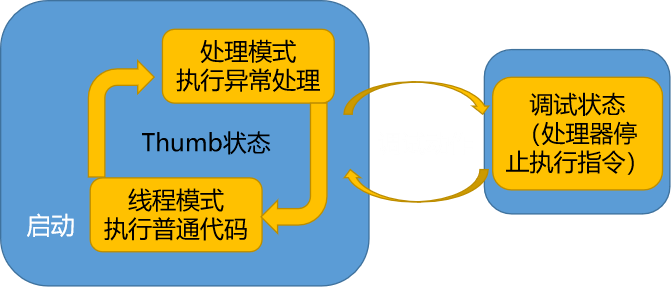

Cortex-M0工作模式

线程模式(Thread Mode):芯片复位后,执行用户程序

处理模式(Handler Mode):当处理器发生了异常或者中断,处理完成后返回线程模式

Cortex-M0工作状态

Thumb状态:正常运行时处理器的状态

调试状态:调试程序时处理器的状态

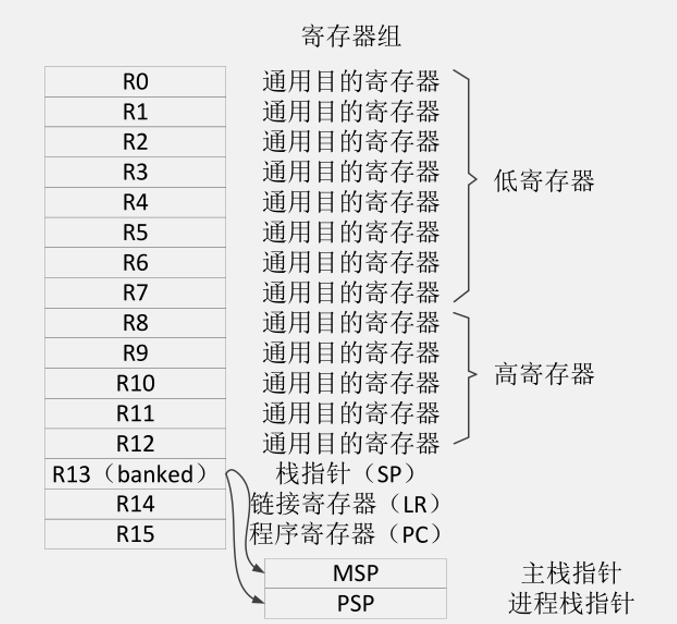

Cortex-M0的寄存器

- R0-R12:13个通用寄存器

- 其中 R0-R7为低端寄存器,可作为16位或32 位指令操作数,R8-R12为高端寄存器,只能用作32位操作数

- R13:栈指针寄存器 SP(the stark pointer)

- Cortex-M0 在不同物理位置上存在两个栈指针,主栈指针 MSP,进程栈指针 PSP。在处理模式下,只能使用主堆栈,在线程模式下,可以使用主堆栈也可以使用进程堆栈。 系统上电的默认栈指针是MSP。这样设计的目的是为了在进行模式转换的时候,减少堆栈的保存工作。同时也可以为不同权限的工作模式设置不同的堆栈。

- R14:链接寄存器LR(the link register)

- 用于存储子程序或者函数调用的返回地址

- R15:程序计数器PC(the program counter register)

- 存储下一条将要执行的指令的地址。

- 特殊寄存器:组合程序状态寄存器xPSR,该寄存器由三个程序状态寄存器组成

- 应用PSR(APSR):保存程序计算结果的状态标志

- N负数标志

- V溢出标志

- C进位借位标志

- Z零标志

- 中断PSR(IPSR):包含当前ISR的异常编号

- 执行PSR(EPSR):包含Thumb状态位

- 应用PSR(APSR):保存程序计算结果的状态标志

- 控制寄存器:CONTROL

- 控制处理器处于线程模式时,使用哪个堆栈

- =0,使用MSP 处理器模式时,固定使用MSP

- =1,使用PSP

Cortex-M0的中断和异常

中断(Interrupts): 中断是由外部事件引起的,它们可以是来自外设的信号,例如定时器到期、串口接收到数据等。

当中断事件发生时,处理器会立即停止当前执行的任务,并转而执行一个与该中断事件相关联的中断处理程序(Interrupt Service Routine,ISR)。ISR是一个预先定义的函数,用于处理特定的中断事件。一旦ISR执行完成,处理器会返回到先前中断发生的地方继续执行。

Cortex-M0支持多个中断优先级,并具有可编程的向量表(Vector Table),它包含了中断向量的地址。当中断事件发生时,处理器会从向量表中找到相应中断的地址,并跳转到ISR执行。

异常(Exceptions): 异常是指处理器在执行指令过程中检测到的错误或特殊事件。异常可以是由于程序错误(例如除以零或无效的指令)引起的,也可以是由硬件事件(例如存储器错误或外设错误)引起的。

Cortex-M0支持多种类型的异常,包括硬件中断、软件中断(通过软件指令触发)、错误中断等。当发生异常时,处理器会立即暂停当前任务,并跳转到一个预定义的异常处理程序(Exception Handler)。异常处理程序是与异常类型相关联的代码块,用于处理异常情况。一旦异常处理程序执行完成,处理器将返回到异常发生的地方继续执行。

Cortex-M0的指令集

ARM处理器支持两种指令集:ARM 和 Thumb。

注:EPSR寄存器的T标志位负责指令集的切换,Cortex-M0只支持Thumb指令。

- ARM指令集

- 32位精简指令集

- 指令长度固定

- 降低编码数量产生的耗费,减轻解码和流水线的负担;

- Thumb指令集

- Thumb指令集是ARM指令集的一个子集;

- 指令宽度16位;

- 与32位指令集相比,大大节省了系统的存储空间;

- Thumb指令集不完整,所以必须配合ARM指令集一同使用