Cortex-M0内核

Cortex-M0处理器的优势

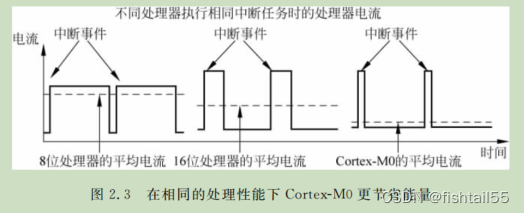

能耗效率:处理器规模大小差不多,但是代码执行效率更高。所以能降能耗。

存储器容量限制

概念:32位能访问的空间肯定比16位,8位访问的空间多。这里不讨论16位的使用分页等操作来扩展存储空间。

代码密度高:Cortex-M0具备多种寻址方式,提高了代码密度。

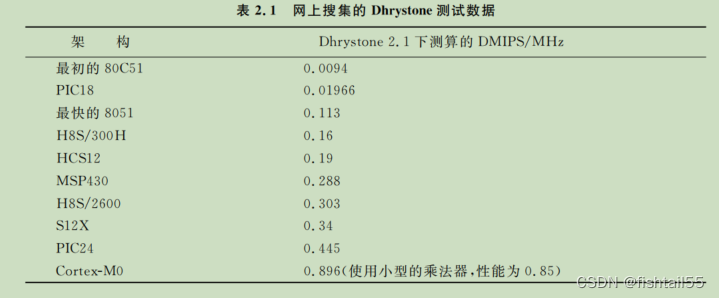

关键字:高性能,程序执行速度快。0.9DMIPS/MHz;

关键字:高代码密度。高代码密度意味着单位代码实现更多功能。

关键字:确定的中断响应时间。最短16个时钟周期。16*1/48MHz = 500ns 左右。

NMI 输入。

概念:不可屏蔽中断。

作用:当系统发生致命故障时,使用该中断。

关键字:请求管理调用。SVC异常和PendSV。

关键字:Cortex-M0 向上兼容Cortex-M3, Cortex-M4;

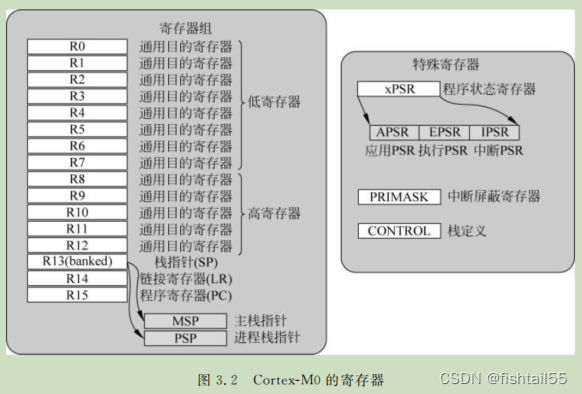

寄存器和特殊寄存器

概念:数据在存储器中和寄存器中反复加载、存储,实现数据处理,称为加载-存储架构。使用内部寄存器操作,对存储器的操作也会减少。如果数据访问涉及到FLASH那么就会减少时间。

栈指针

概念:R13,栈指针(SP); 在不同的物理位置上存在两个栈指针。主堆栈指针(MSP)和进程堆栈指针(PSP);使用CONTROL来切换。

应用场景:栈一般是程序进中断的时候,会使用栈。或者在线程模式时,临时变量太多,内部寄存器不够用了,那么会使用栈。

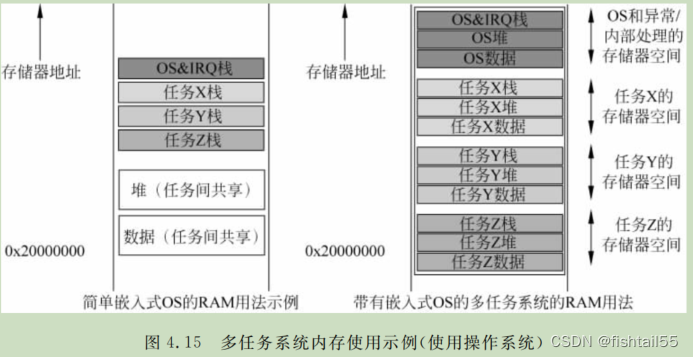

主堆栈指针和进程栈指针的切换场景:一般不用切换。操作系统会涉及到切换,这是因为系统内核的占空间和线程级的栈空间是相互独立的。

xPSR,组合程序状态寄存器

概念:提供了程序执行信息和ALU(算术逻辑单元)标志。该寄存器由三个程序状态寄存器组成。APSR、IPSR、EPSR。

作用:指示的东西比较少,一般不用去看。涉及到程序跳转控制,数学计算。

PRIMASK 中断屏蔽特殊寄存器

概念:置位后,除了NMI和Hardfault之外的中断都会被屏蔽掉。实际上,此时当前的中断优先级被置为了0,这也是可以配置的最高等级。

与此类似的还有:faultmask,连fault都关闭。basepri; 控制屏蔽的中断优先级,rtos中常用。

本质:改变当前中断优先级为最高,导致其他中断优先级不回被响应了。

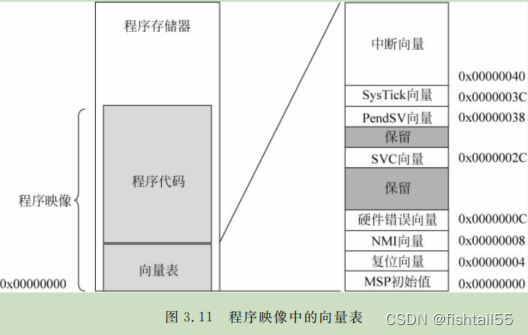

程序映像

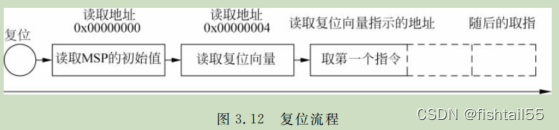

概念:程序映像就是程序的执行地址。从0x0000000开始,获取向量表。向量表关键的是前两个地址,0x0000000和0x00000004,存储MSP栈地址和复位向量地址。

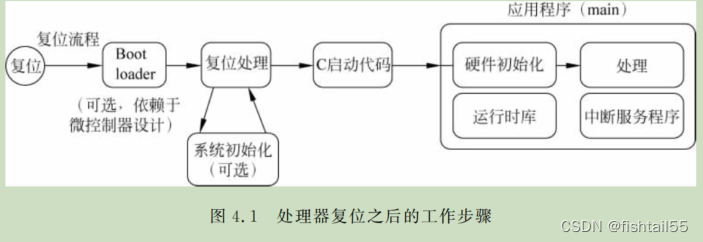

启动流程

嵌入式程序设计

常见的程序结构:轮询、中断、轮询中断混合,RTOS;

难点:并发任务的处理

场景:多个任务同时需要执行,其中一个任务过长,执行时间很长,导致其他几个任务不能得到及时响应而后程序失败。

解决办法:1、大任务切片划分。2、RTOS;

1、大任务切片划分,如果应用程序非常复杂的时候,手动拆分任务就不切实际了。

2、RTOS会有时间片的概念,自动在时间片结束后执行任务切换。在Freertos中需要手动打开。

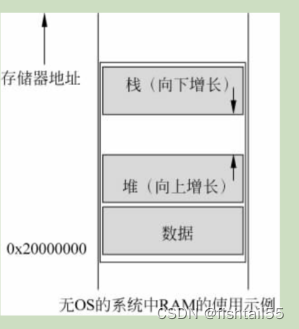

RAM 空间组织

数据区域:包含全局变量和静态变量。

栈区域 :用于临时数据存储、局部变量的存储空间、函数调用参数传递和异常处理处理的寄存器备份。突出一个临时。

Q:函数传参是怎么实现的?A:函数参数太多了,内部寄存器不够用了,也就放到栈里了。

堆区域 : C函数自动分配存储器区域,例如malloc。

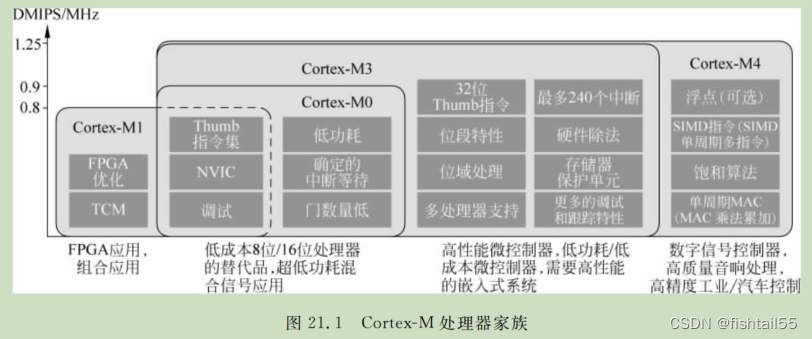

Cortex-M 处理器的差别

M3比M0多:

支持MPU(存储器保护单元);

指令集更丰富;如除法器;

NVIC更灵活,优先级可变换。

调试方面,断点更多,支持跟踪特性;

架构

Cortex-M0是冯诺依曼架构。

Cortex-M3是哈佛架构。

冯架构和哈佛架构的区别是:指令寻址和数据寻址是否走同一条总线,走同一条总线的是冯诺依曼架构,走两条总线的是哈佛架构。